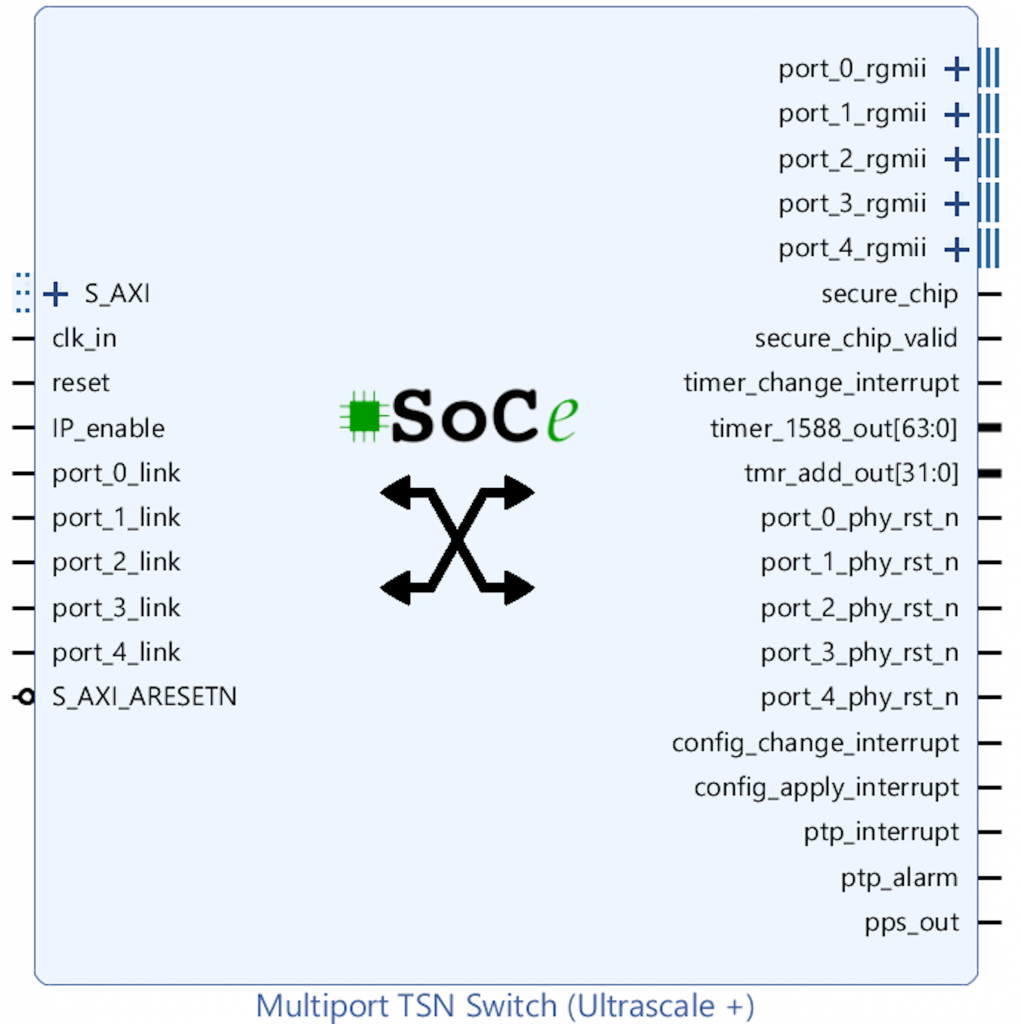

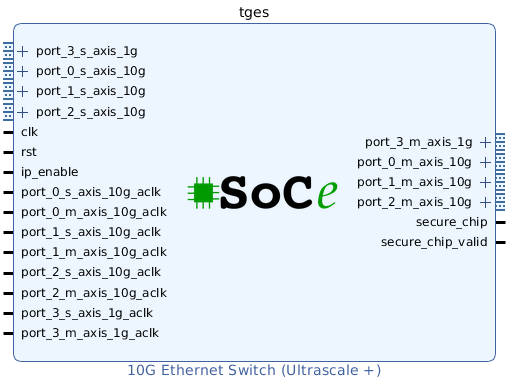

1G MTSN-多端口TSN交换机IP核

接口

- 全双工10/100/1000 Mbps以太网接口

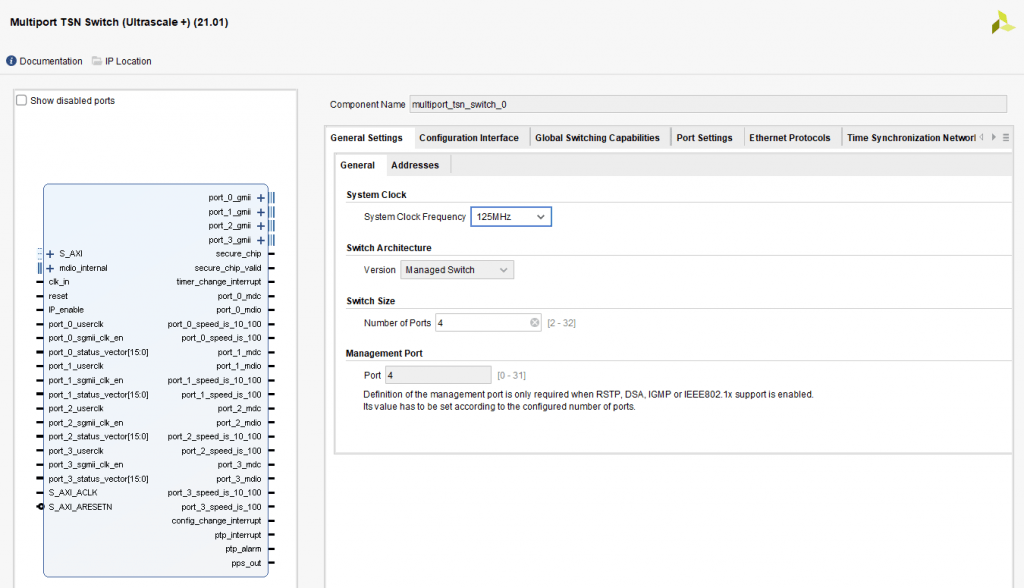

- 最多可配置32个以太网端口

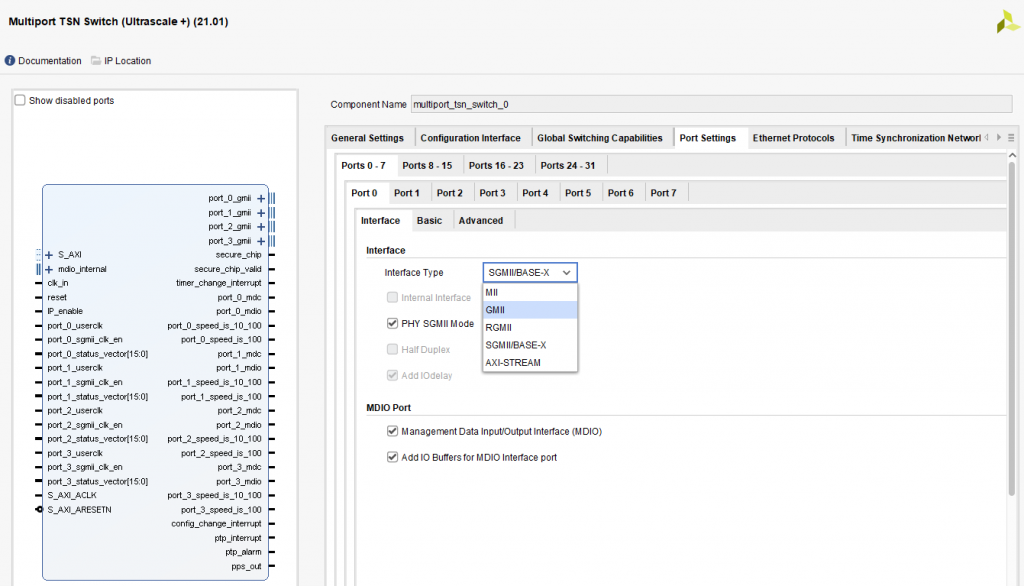

- MII/RMII/GMII/RGMII/SGMII/QSGMII物理层设备(PHY)接口

- 每个端口支持不同的数据速率

交换

- 具有自动MAC地址学习和老化(最多4096个条目)的动态MAC表

- 静态MAC表(最多4096个条目)

- 巨型帧管理

- 广播/多播风暴防护

- 每端口速率限制(广播、多播和单播流量)

- 基于端口的VLAN支持

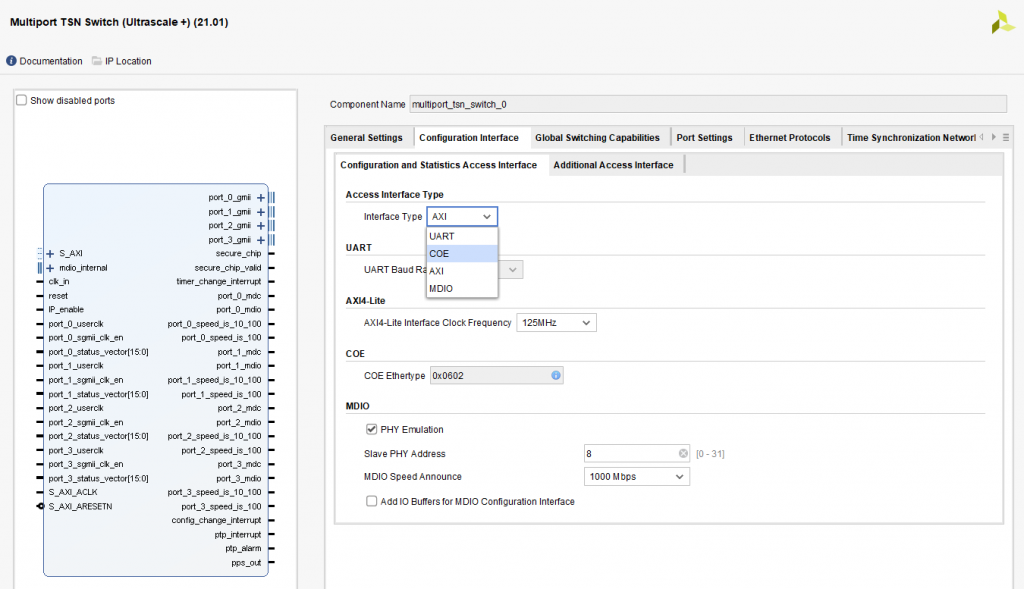

低层配置

- MDIO、UART、AXI4-lite或CoE管理接口。

- 以太网配置(CoE):通过连接到CPU的同一以太网链路全面访问内部寄存器

- 购买IP核时提供驱动程序

高级配置

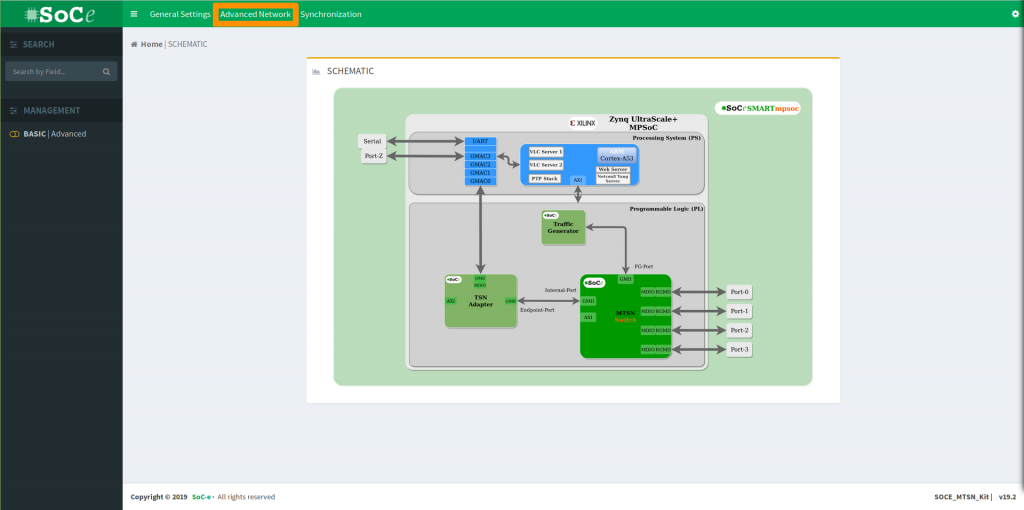

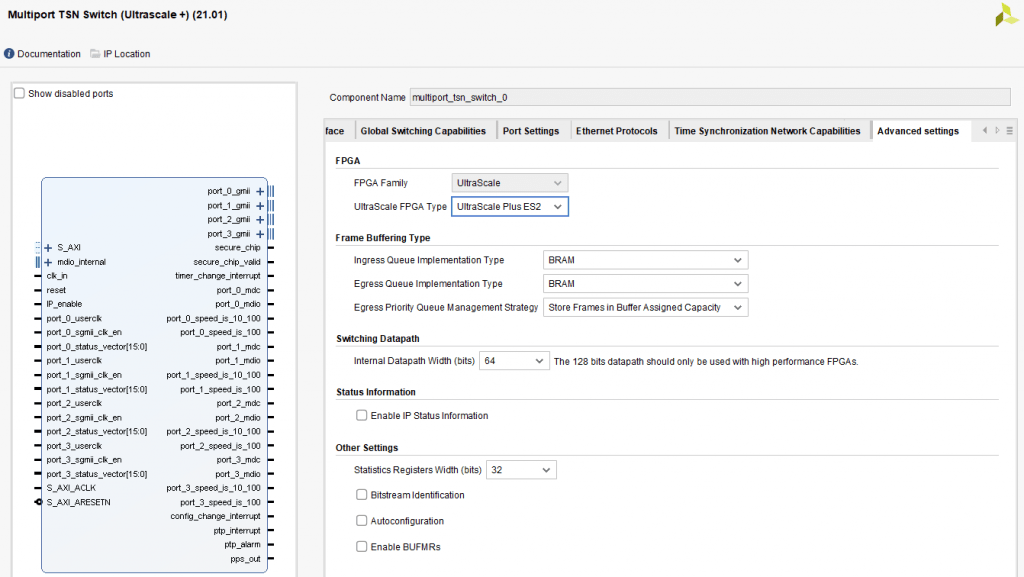

- 板载UltraScale™ FPGA,用于高速网络交换和PTP时间戳

- 多核CPU单元支持自主软件应用

时间敏感网络

- IEEE 802.1AS(rev)用于时间同步层

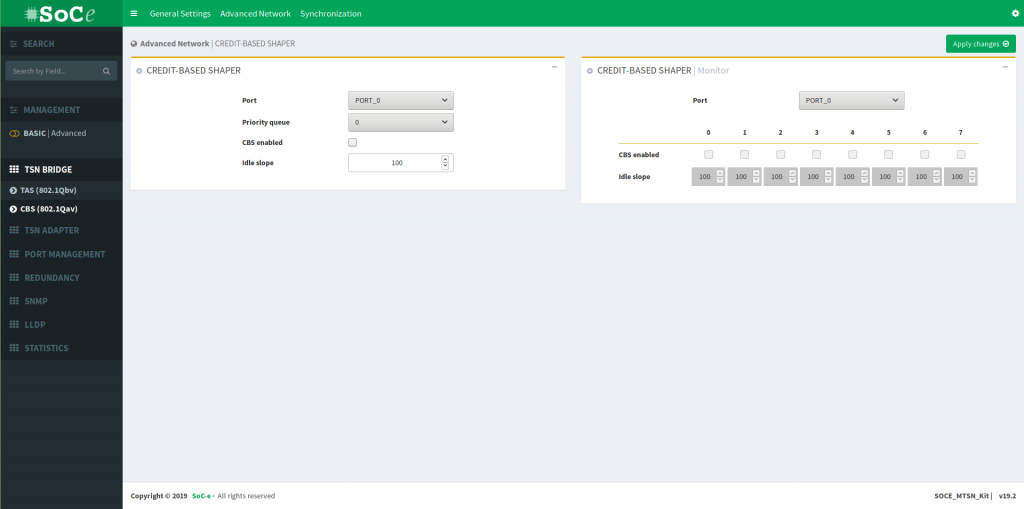

- IEEE 802.1Qav用于预留流量

- 基于信用的整形器:可为每种流量类别配置带宽预留

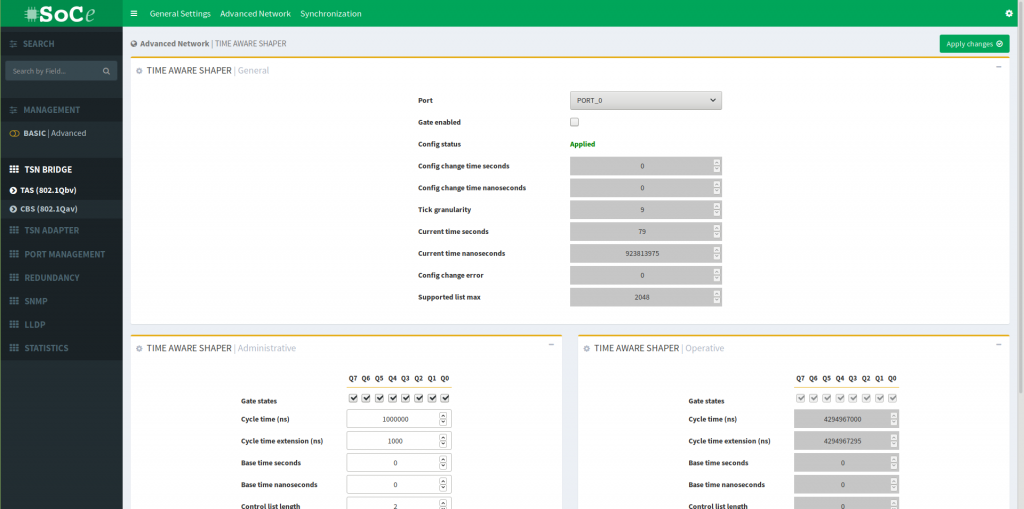

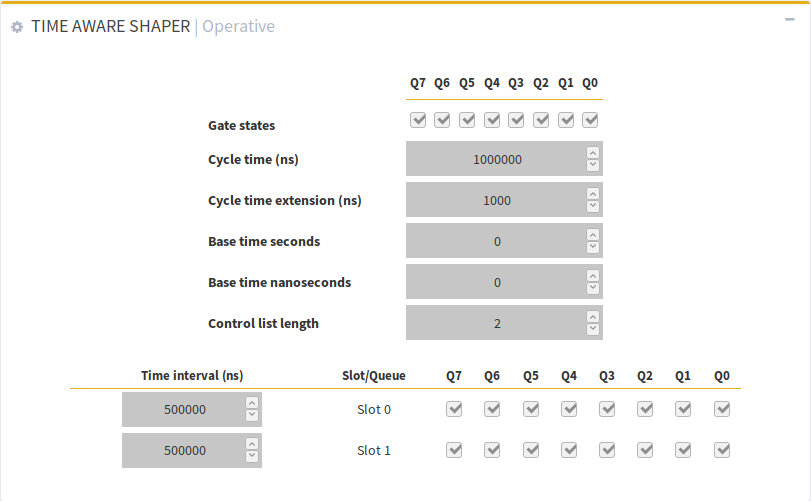

- IEEE 802.1Qbv用于计划的流量

- 时间感知整形器:可配置的时隙数量

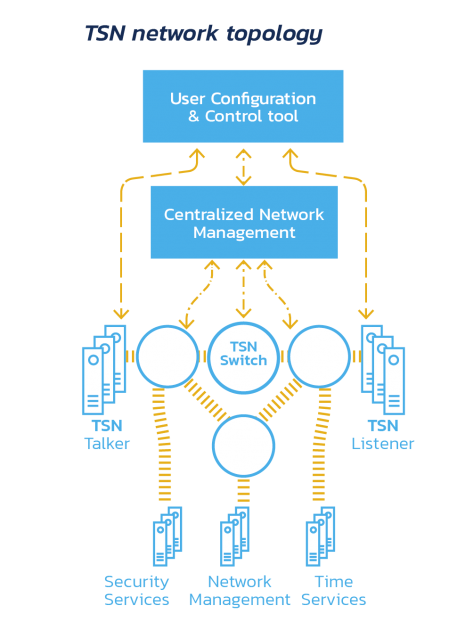

- IEEE 802.1Qcc用于网络管理

- NETCONF用于掌管YANG数据

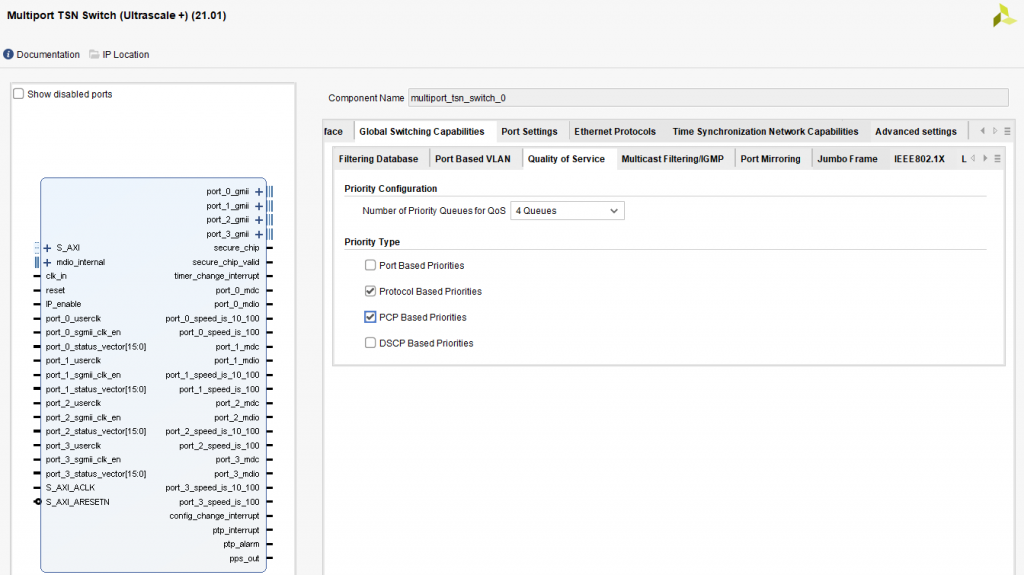

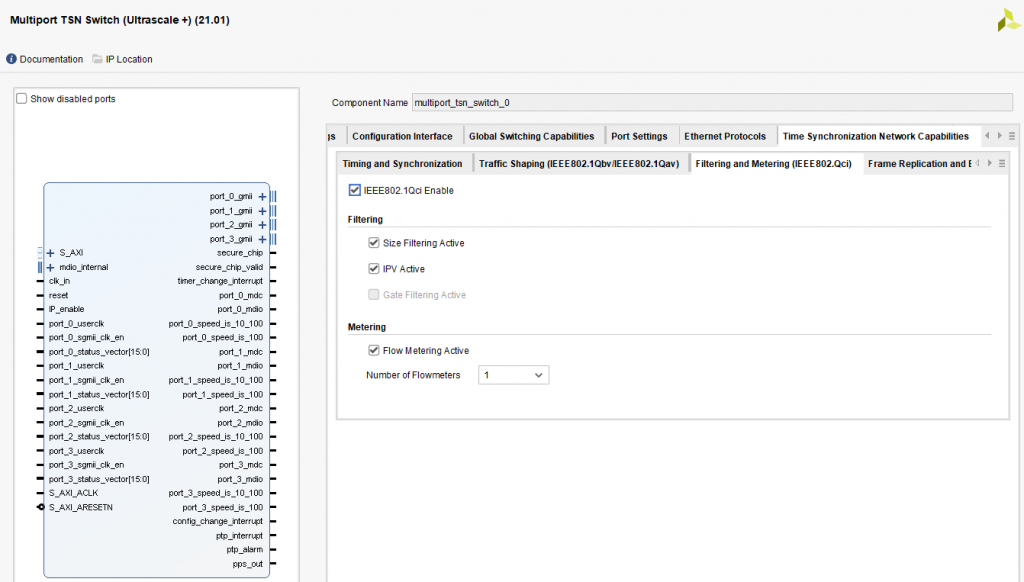

- IEEE 802.1Qci用于数据流过滤和监管

- IEEE 802.1AB用于LLDP(链路层探测协议)

- IEEE 802.1w用于快速生成树协议

- IEEE 802.1s用于多生成树协议

- IEEE 802.1CB用于帧复制和可靠性消除(*)

- 对同步调度流量的直通支持(*)

- IEEE 802.1Qbu/802.3br用于帧抢占(*)

*未来版本或互操作性测试待定

支持的Xilinx FPGA评估板

我们的 MTSN IP 内核可部署在以下 Xilinx 系列中。您可以在以下链接中找到不同的 Xilinx 产品表和选择指南:

- 7 系列(Zynq、Spartan、Artix、Kintex、Virtex)

- Ultrascale(Kintex、Virtex)

- Ultrascale+(Zynq MPSoC、Kintex、Virtex)

- Versal ACAP

此外,我们还开发了网络模块上的系统或网络模块。在这种情况下,我们为需要使用一体化解决方案来为其设备中引入时间敏感网络的客户提供M TSN套件解决方案。

与时俱进 锐意创新——与虹科一起探索TSN的更多潜力

时间敏感网络(Time Sensitive Networking,TSN) ,是基于标准以太网架构演进的新一代网络技术,它以传统以太网为网络基础,通过时钟同步、数据调度、 网络配置等机制,提供确定性数据传输能力的数据链路层协议规范。与传统以太网相比,TSN能够提供微秒级确定性服务,降低整个通信网络复杂度,实现信息技术 (IT)与运营技术(OT)融合,其具有精准的时钟同步能力、确定性流量调度能力,以及智能开放的运维管理架构,可以保证多种业务流量的共网高质量传输, 兼具性能及成本优势,是未来网络的发展趋势。

目前,TSN技术在汽车、工业、轨道交通、航空航天领域有着较高的讨论热度,它作为一项非供应商绑定的实时通讯协议,我们认为TSN技术有着不错的应用前景。

欢迎联系我们与您一起探讨学习TSN技术与各行各业的结合,并积极推动更多落地应用,共同构建智能互联的新世界。