1G UES

非网管以太网交换机IP核

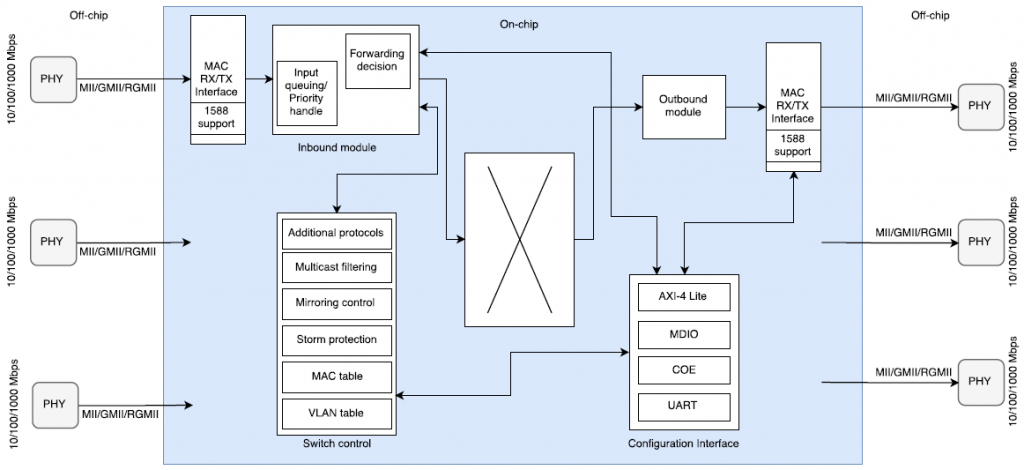

非网管以太网交换机IP核(UES)在可配置设备上实现了即插即用的以太网交换。它不需要外部配置,旨在使用最少的资源解决最大的吞吐量。

- 即插即用:无需配置

- 高性能:在端口之间实现全交叉矩阵,以实现最大吞吐量

- 快速:得益于 SoC-e 专有的 MAC 地址匹配机制,延迟时间大大缩短

- 高效:经过优化,只需很少的逻辑资源,即可在低成本 FPGA 设备上实现

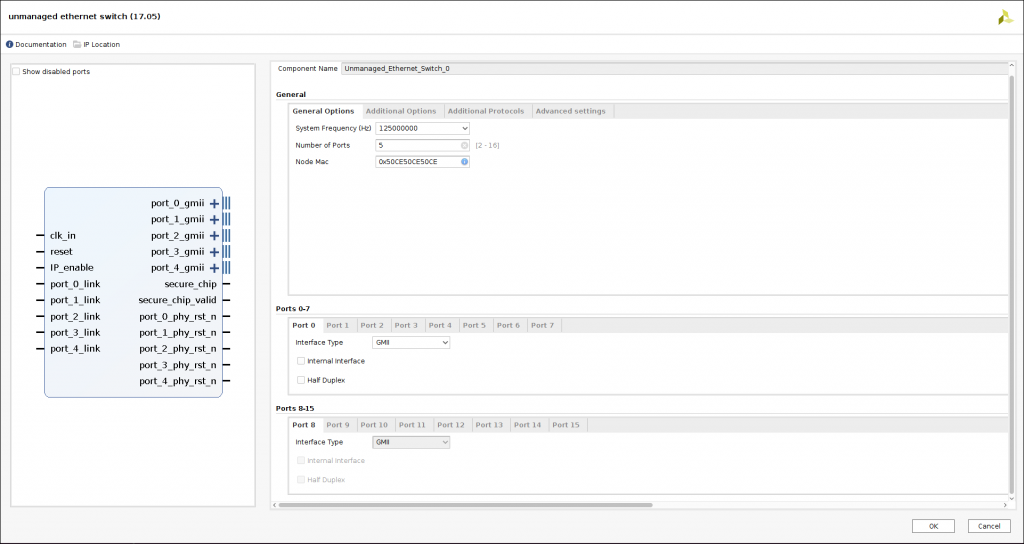

- 灵活: 完全可扩展和可配置,以实现最佳功能大小的权衡。以下参数可用于设计器:

- 端口数:可配置的 3 到 32 个以太网端口

- 缓冲区队列长度

- IEEE 透明时钟功能

- 自动:MAC 地址学习和老化(默认情况下,存储容量为 2048 个 MAC 地址)。