在本篇文章中,我们将展示两种可在FPGA上实现的COTS IEC 62439-3交换机IP核的延迟的比较。第一种是混合使...

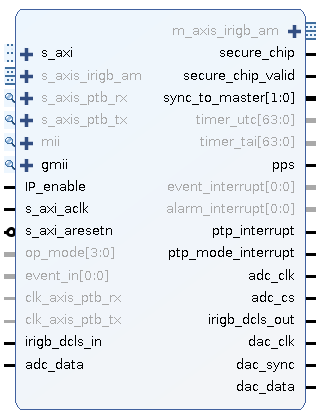

SOC-E SocTek系列

MTSN IPcore

全面的TSN开发方案,能够实现多种TSN协议规范

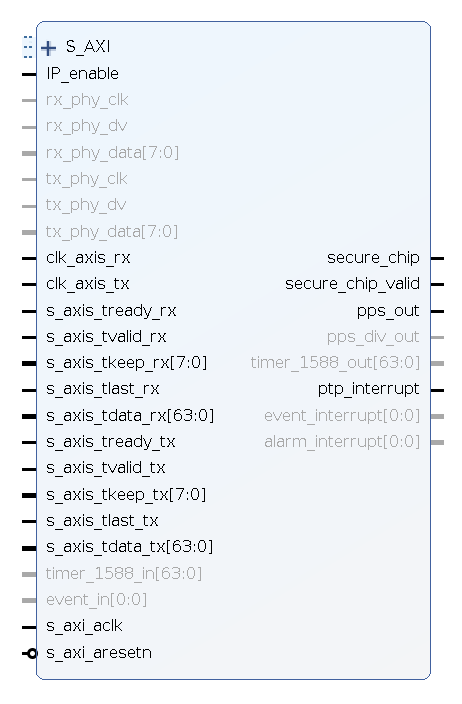

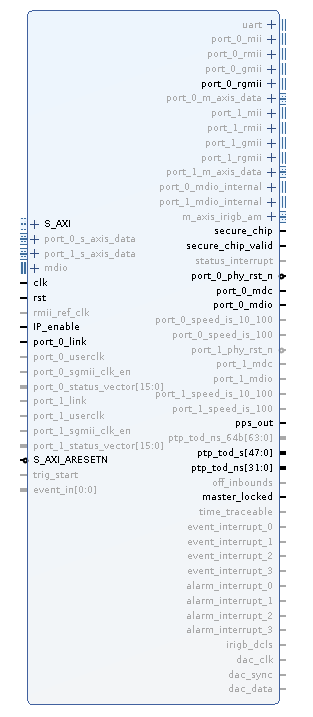

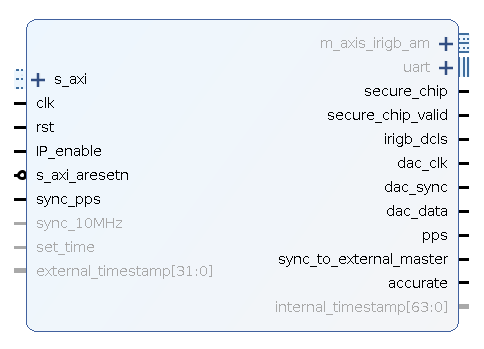

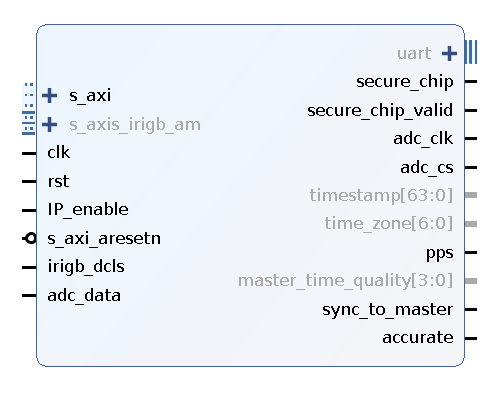

SOC-E SocTek系列MTSN IP核是一个灵活的HDL代码,可以生成TSN端点或TSN桥接实现。该IP提供了一组丰富的通用参数,以获得最佳的功能资源权衡。由于Vivado IPI提供了GUI界面,因此可以在VHDL级别或以图形方式配置这些通用项目。

- 多种PHY接口可选:MII/RMII/GMII/RGMII/SGMII/QSGMII

- 交换能力:全双工10/100/1000 Mbps以太网接口;最多可达32端口,每个端口支持不同的数据速率

- IP核配置端口:4 种配置管理端口