10G MTSN-多端口TSN交换机IP核

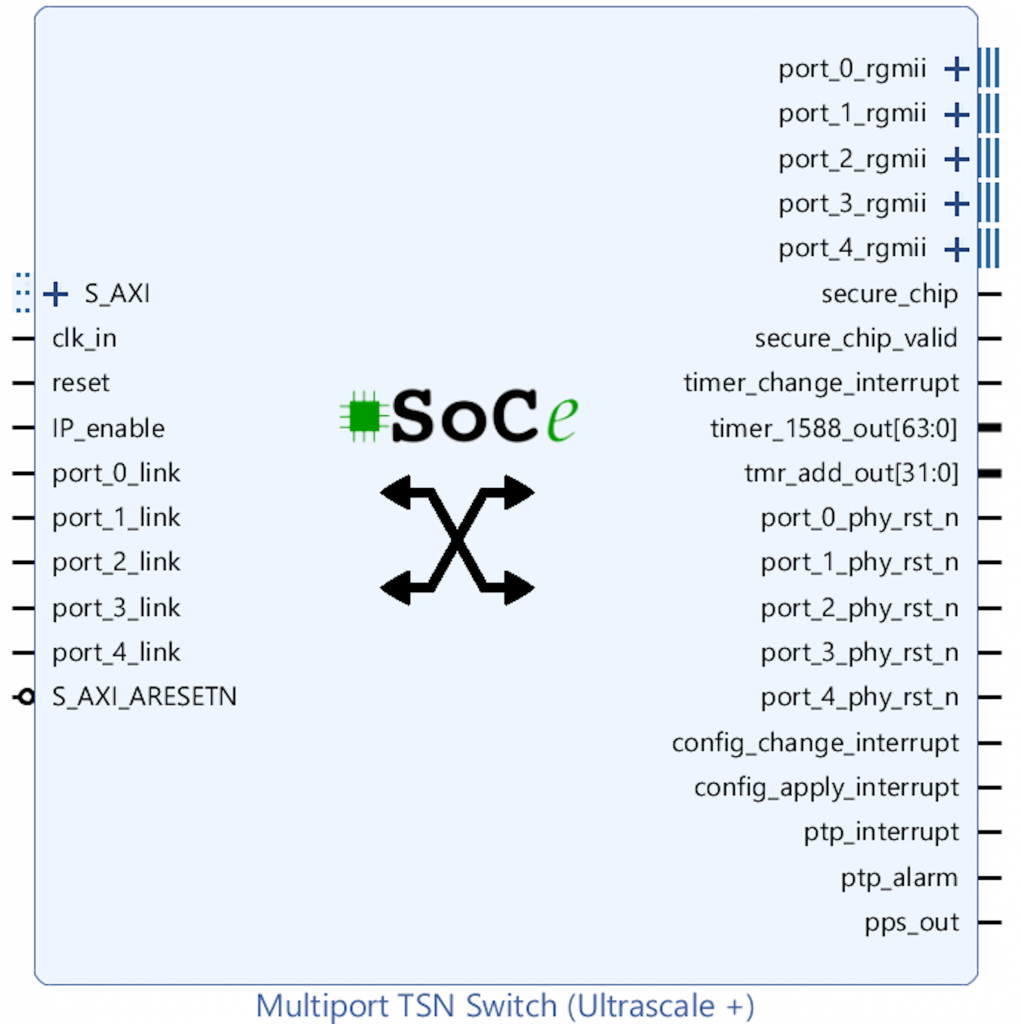

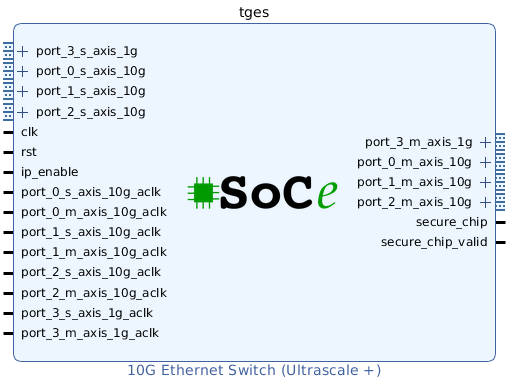

接口

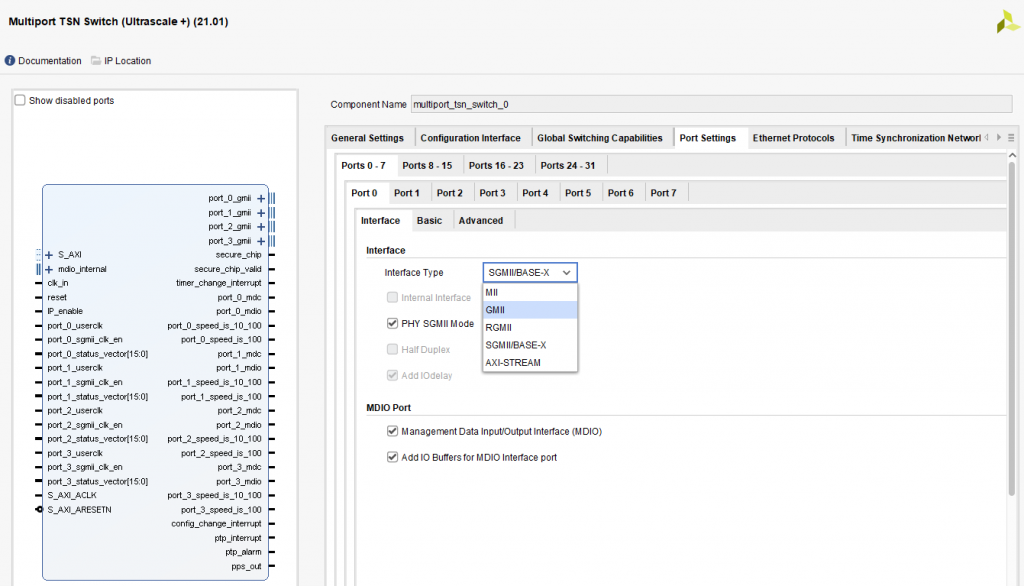

- 全双工100M/1G/2.5G/5G/10G以太网接口

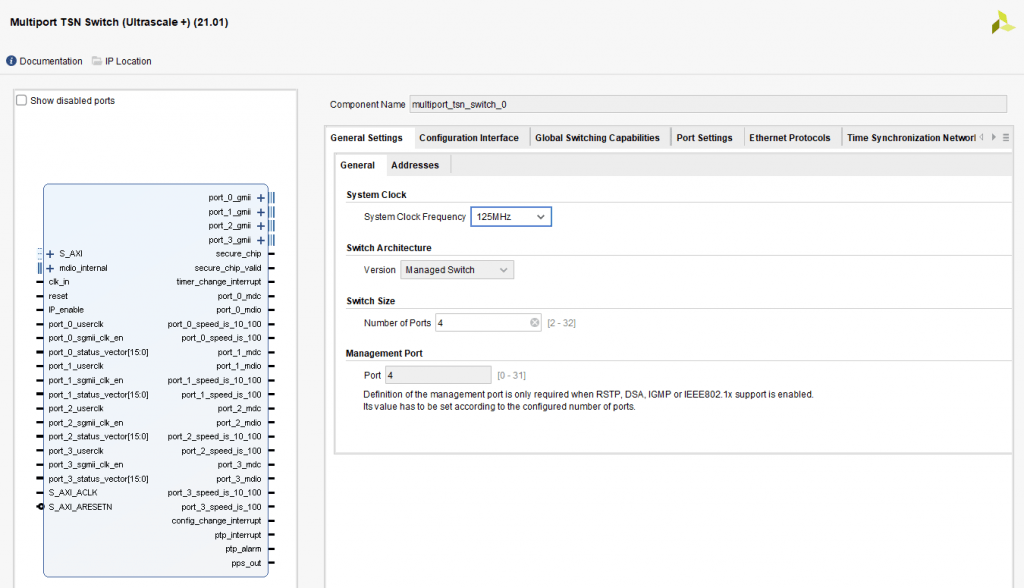

- 最多可配置32个以太网端口

- MII/RMII/GMII/RGMII/SGMII/QSGMII/USXGMII 物理层设备 (PHY) 接口。(其他请联系我们)

- 每个端口支持不同的数据速率

交换

- 具有自动MAC地址学习和老化的动态MAC表

- 静态MAC表

- 巨型帧管理

- 广播/多播风暴防护

- 每端口速率限制(广播、多播和单播流量)

- 基于端口的VLAN支持

低层配置

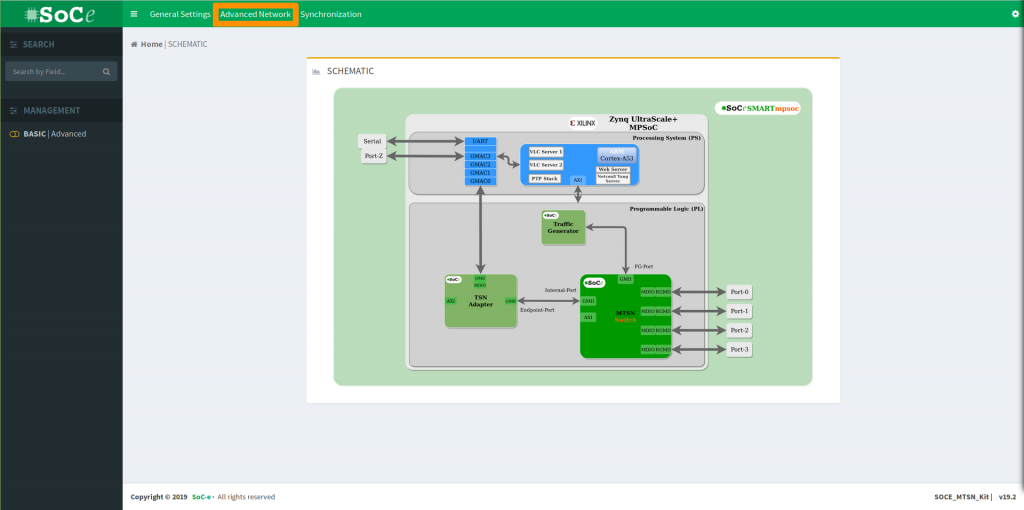

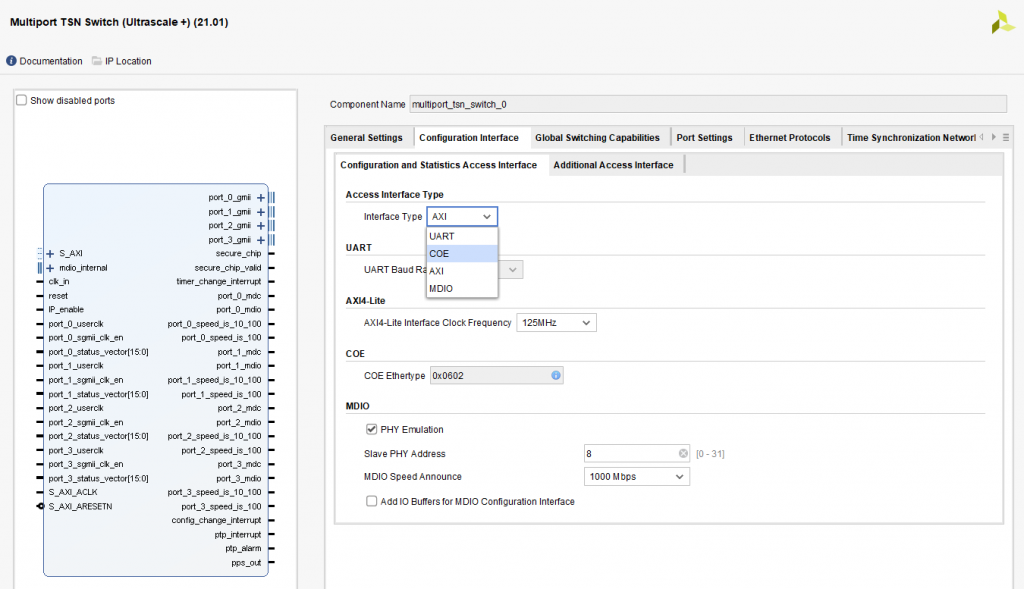

- MDIO、UART、AXI4-lite管理接口。

- 购买IP核时提供驱动程序

高级配置

- NETCONF YANG模型支持(CNC配置)

- 高级配置GUI

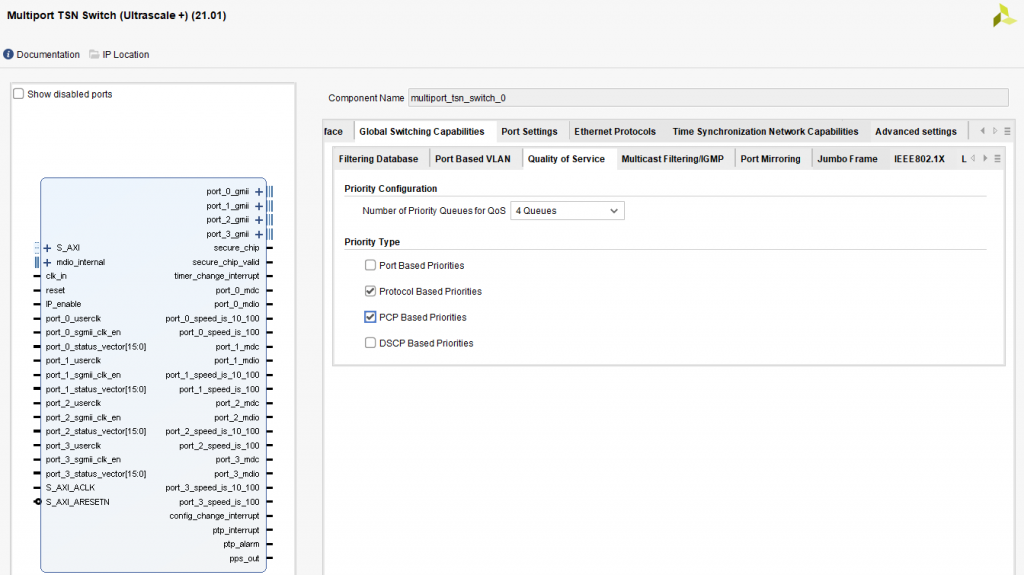

时间敏感网络

- IEEE 802.1AS(rev)用于时间同步层

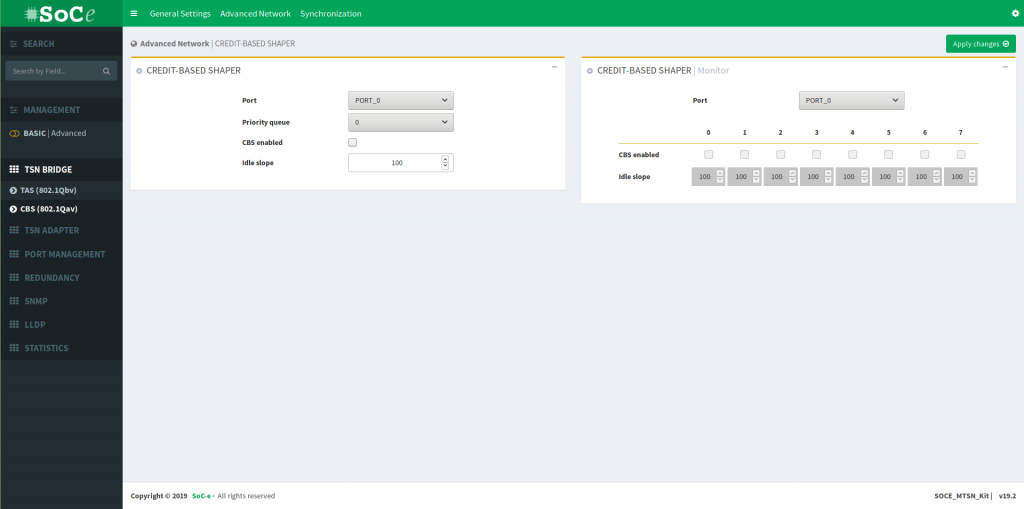

- IEEE 802.1Qav用于预留流量

- 基于信用的整形器:可为每种流量类别配置带宽预留

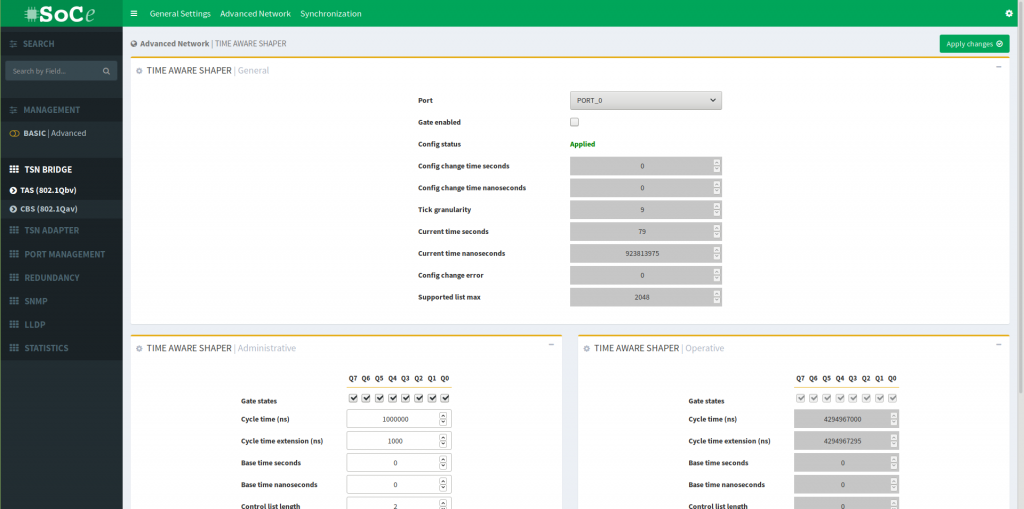

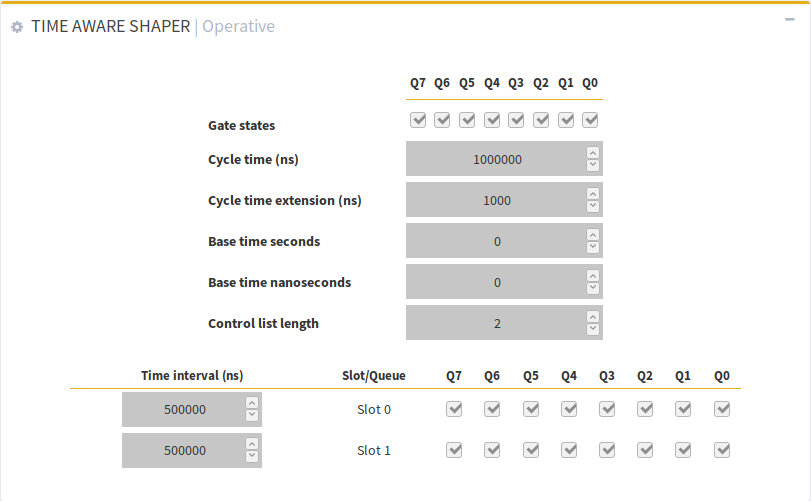

- IEEE 802.1Qbv用于计划流量

- 时间感知整形器:可配置的时隙数量

- IEEE 802.1Qcc用于网络管理

- NETCONF用于掌管YANG数据

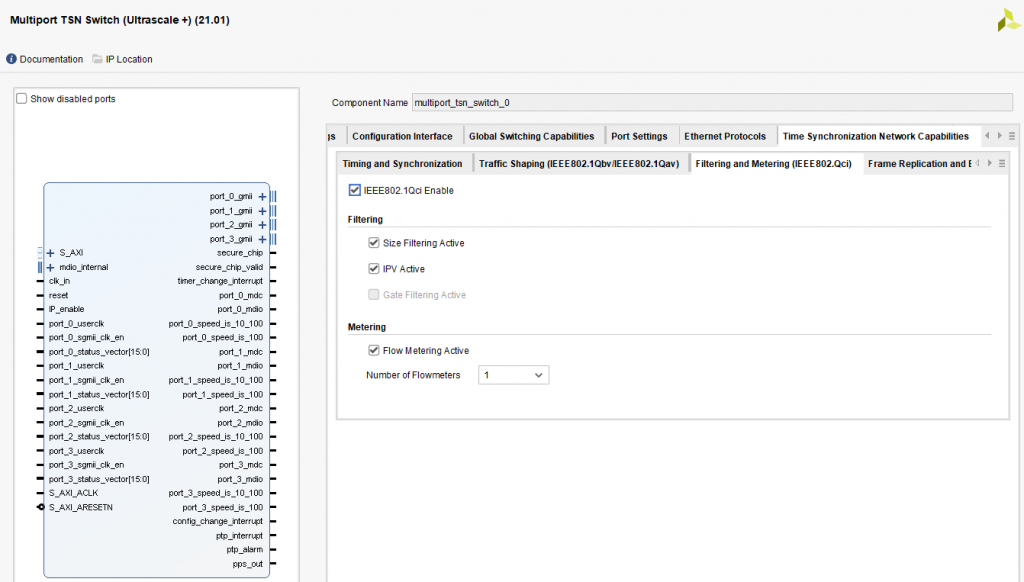

- IEEE 802.1Qci用于数据流过滤和监管(*)

- IEEE 802.1AB用于LLDP(链路层发现协议)

- IEEE 802.1w快速生成树协议

- IEEE 802.1s多生成树协议

- IEEE 802.1CB帧复制和可靠性消除(*)

- IEEE 802.1Qbu/802.3br帧抢占(*)

*未来版本或互操作性测试待定

支持的Xilinx FPGA评估板

虹科10G MTSN IP 内核可部署在以下 Xilinx 系列中。您可以在以下链接中找到不同的 Xilinx 产品表和选择指南:

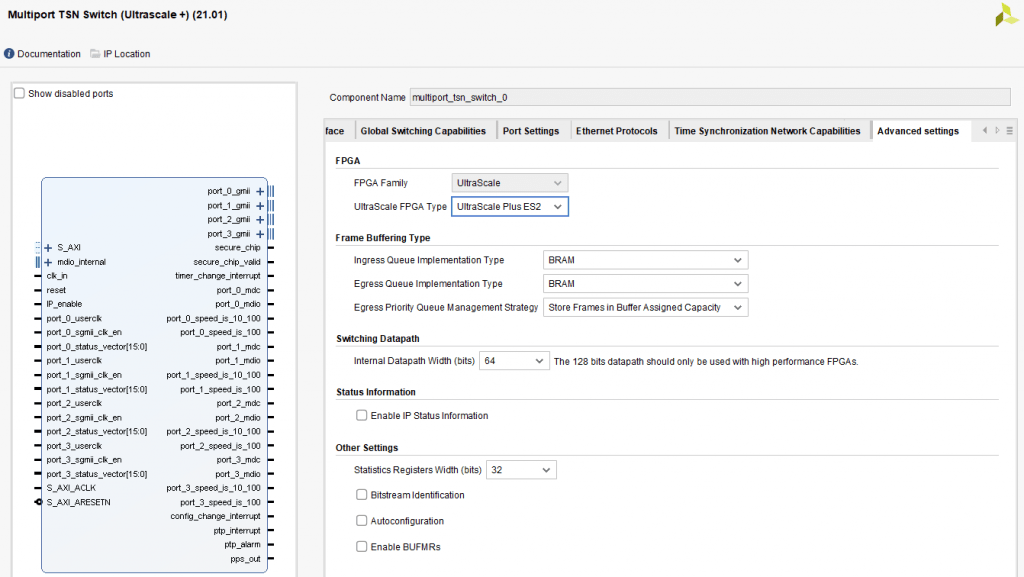

- 7 系列(Zynq、Spartan、Artix、Kintex、Virtex)

- Ultrascale(Kintex、Virtex)

- Ultrascale+(Zynq MPSoC、Kintex、Virtex)

- Versal ACAP

在评估板方面,我们还推出了系统级模块( SoM ),可提供SoC-e 的 IP 内核的预加载设计。SoC-e 可以提供基于 7 系列、Ultrascale 或 Ultrascale+ Xilinx FPGA 系列的 SoM。

与时俱进 锐意创新——与虹科一起探索TSN的更多潜力

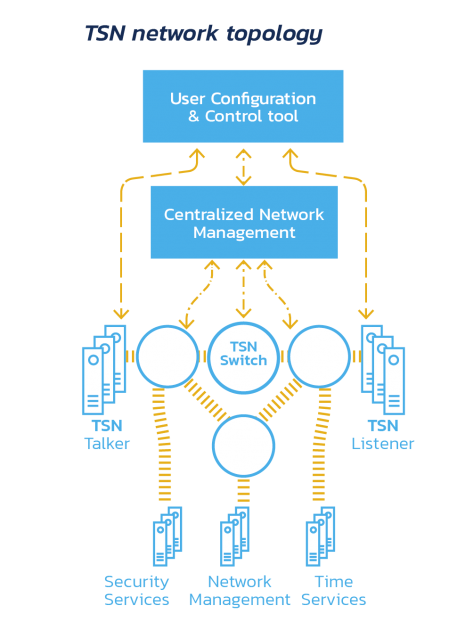

时间敏感网络(Time Sensitive Networking,TSN) ,是基于标准以太网架构演进的新一代网络技术,它以传统以太网为网络基础,通过时钟同步、数据调度、 网络配置等机制,提供确定性数据传输能力的数据链路层协议规范。与传统以太网相比,TSN能够提供微秒级确定性服务,降低整个通信网络复杂度,实现信息技术 (IT)与运营技术(OT)融合,其具有精准的时钟同步能力、确定性流量调度能力,以及智能开放的运维管理架构,可以保证多种业务流量的共网高质量传输, 兼具性能及成本优势,是未来网络的发展趋势。

目前,TSN技术在汽车、工业、轨道交通、航空航天领域有着较高的讨论热度,它作为一项非供应商绑定的实时通讯协议,我们认为TSN技术有着不错的应用前景。

欢迎联系我们与您一起探讨学习TSN技术与各行各业的结合,并积极推动更多落地应用,共同构建智能互联的新世界。