博客

数据接口

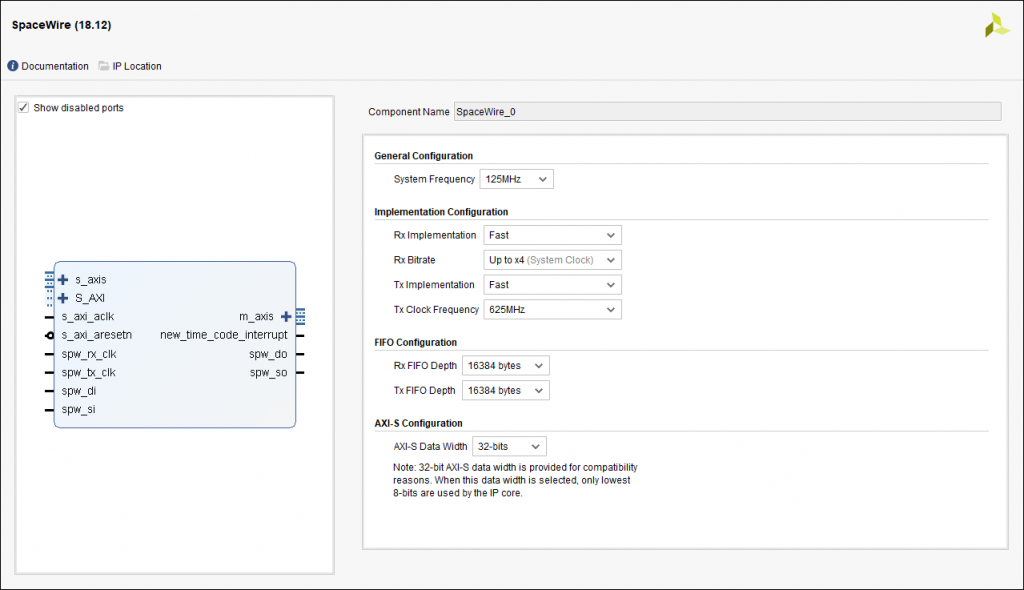

- Rx 比特率高达系统时钟频率的 x4

- Tx 时钟频率在 100MHz-625MHz 之间

- 单独的 clock domains

FIFO 配置

- Tx FIFO 深度完全可配置:从 64 字节到 16384 字节

- Rx FIFO 深度完全可配置:从 64 字节到 16384 字节

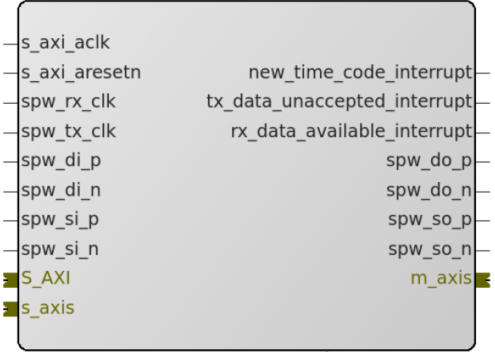

接口

- AXI-Stream (数据)

- AXI-4 Lite (配置与管理)

性能

- 高达 200Mbps 的链接速度

SOC-E的SMARTcia板可支持SpaceWire IP核,专用于空间环境的一个平台,可满足当前法规要求。

有关此IP、许可模式和基于此标准的交钥匙项目的更多信息,请联系我们:info@hkaco.com。

可用于Xilinx Vivado工具的SOC-E SocTek系列SpaceWire IPcore

通过利用新的Xilinx Vivado工具,可以将SOC-E SocTek系列SpaceWire IP无缝集成到您的FPGA设计中,该工具允许在图形用户界面中使用IP内核并以简单的方式配置IP参数。

以下Xilinx和Microchip FPGA系列支持SOC-E SocTek系列SpaceWire IP:

- 7 系列(Zynq、Spartan、Artix、Kintex、Virtex)

- 超大规模(Kintex、Virtex)

- Ultrascale+(Zynq MPSoC、Kintex、Virtex)

- XQR 系列(航天级 FPGA):Virtex-5QV 和 Virtex

- PolarFire & PolarFire SoCMicrochip 的 FPGA

SOC-E SocTek系列产品推荐

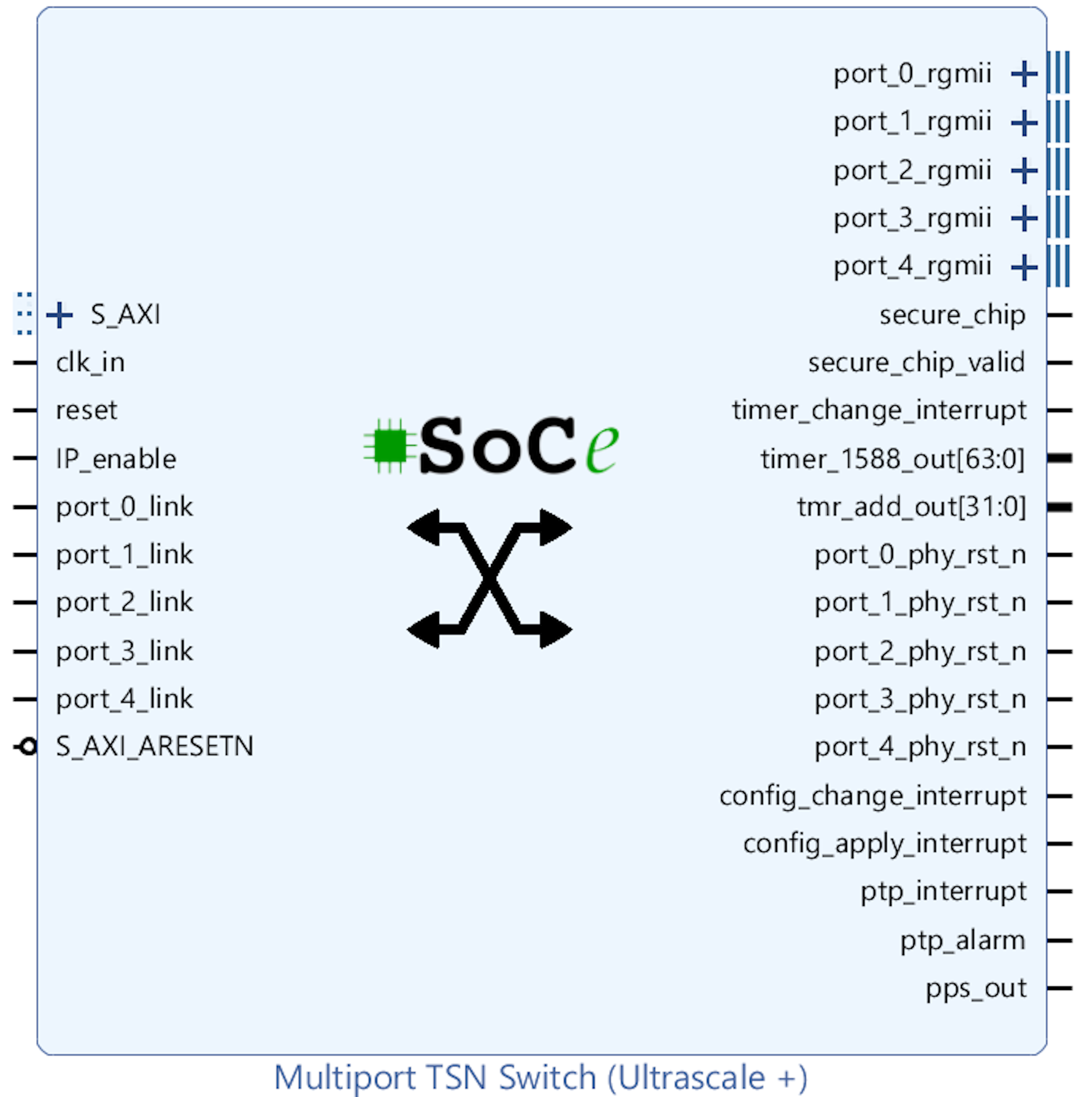

MTSN IPcore

全面的TSN解决方案,能够实现多种TSN协议规范

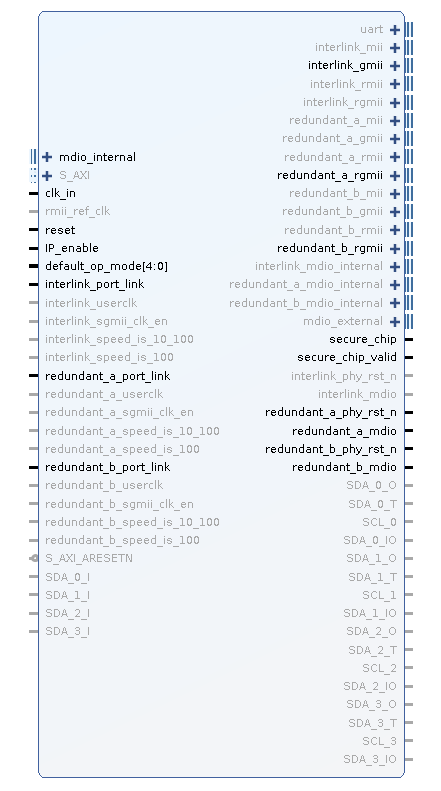

HSR/PRP/PTP IPcore

实现可靠性以太网通信的高可用性无缝冗余和并行冗余协议标准

网管/非网管IPcore

以太网交换机 IP 内核,面向可编程硬件平台

更多IPcore方案

减少设计和调试时间,加速开发进程