博客

虹科干货 | 如何测试与验证复杂的FPGA设计(1)——面向实体或块的仿真

通过在每个输入信号上生成激励并验证 RTL 代码行为是否符合预期,对构成每个 IP 核的不同模块进行实体/块的仿真

“面向实体或块的仿真”这一步骤意味着验证在 IP 核内具有特定操作的特定实体或模块的正确操作。每个 IP 核都由许多实体或块组成,为了测试它们,每个实体会有不同的测试平台,通过在输入受到刺激时观察设计的输出来执行设计。这将有助于检查预期的行为。

举个例子就可以很好地理解一切。在这种情况下,我们将解释虹科以太网交换机IP核的过滤数据库。

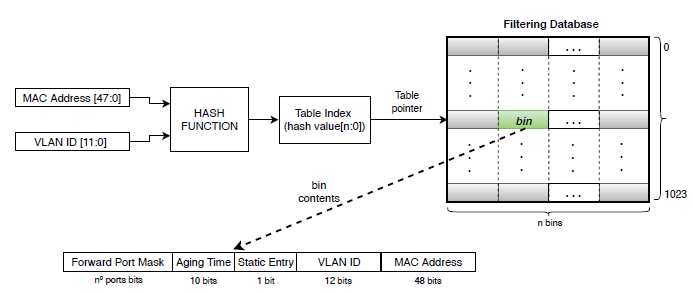

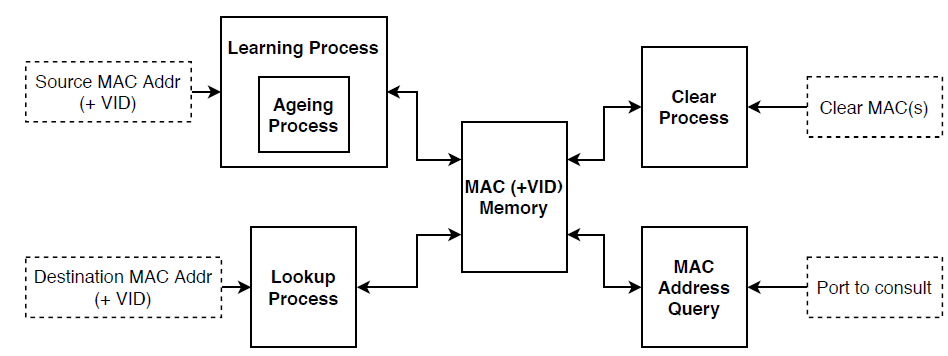

过滤数据库存储 MAC 地址及其相关信息以做出帧转发决策。它是一个基于哈希的存储器,每个地址条目都有一些存储过滤数据的 bin。该哈希算法还生成过滤数据库内存的索引。

过滤数据库执行有三个主要过程:学习、查找和老化。

- 学习过程负责在满足不同条件时保存帧。

- 查找过程是在过滤数据库中搜索并获得帧的转发端口掩码的过程。

- 老化过程根据给定的时间段删除旧的 MAC 条目。

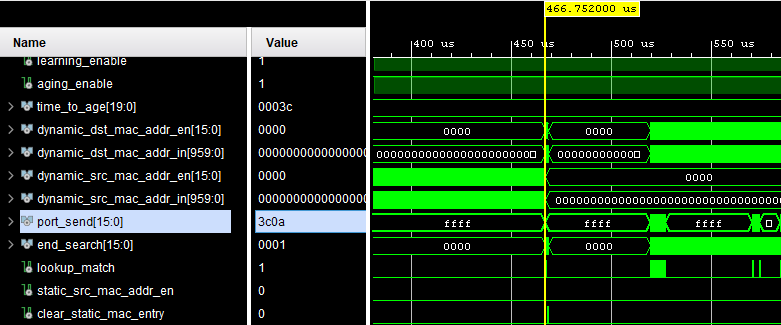

在这个仿真MAC表的具体案例中,请始终尝试测试构成过滤数据库功能的所有机制。从这个意义上说,就像学习不同的MAC,不同的查询、老化是并行完成的,最后需要清除MAC表并验证所有条目都已删除。此外,研究并始终能够测试可能的corner案例也十分重要。

测试和验证复杂 FPGA 设计的第二个关键步骤将在后续更新的文章中展开介绍。一旦形成 IP 核的所有实体都按预期工作,全局仿真就会发挥作用。

IP核可以使开发人员减设计工作量并缩短产品上市时间。虹科目前已有丰富的IP核产品组合,包括TSN IP核、HSR/PRP IP核、以太网IP核、冗余IP核等,可以轻松集成到用户的FPGA中。若想了解更多信息,欢迎点此了解详情或直接联系虹科销售人员

近期文章

- 虹科免费直播 | 精通CAN总线分析:虹科PCAN-Explorer6实战训练营

- 虹科免费直播 | CAN XL研讨会:多位CAN XL创始成员带您解锁CAN XL的巨大能量!

- 虹科应用|煤矿机械数据传输监测难?试试虹科PCAN优选方案

- 虹科新闻|新合作启航,服务如初!虹科与HMS及PEAK合作升级

- 虹科方案|CAN(FD)/LIN远距离通信,难题何解?

- 以太网分析仪netANALYZER Scope软件介绍

- 虹科干货 | 无需外部Redbox即可无缝合并PRP和HSR网络实现时间同步

- 虹科干货 | 解决连接到IEEE 1588高可用性网络的SCADA系统的NTP同步参考问题

- 虹科案例 | 使用PRP协议解决广播行业中实现高可用性和亚微秒同步的难题

- 虹科方案|从CAN到以太网:车载网络数据采集方案

搜索内容

订阅邮件

想要获取虹科最新资讯?欢迎订阅我们的邮件简报!

更多推荐

Menu